## High Quality Factor and High Self-Resonant Frequency Monolithic Inductor for Millimeter-Wave Si-based IC's

D. Dubuc<sup>(1)</sup>, É. Tournier<sup>(1)</sup>, I. Telliez<sup>(2)</sup>, T. Parra<sup>(1)</sup>, C. Boulanger<sup>(3)</sup> and J. Graffeuil<sup>(1)</sup>

<sup>(1)</sup> LAAS / CNRS and University P. Sabatier, 31 077 TOULOUSE. FRANCE.

<sup>(2)</sup> STMicroelectronics, F-38926 CROLLES. FRANCE.

<sup>(3)</sup> CNES, 31401 TOULOUSE. FRANCE.

**Abstract** — Substrate losses of inductors realized with a SiGe BiCMOS technology ( $\rho_{\text{substrate}}=15 \Omega\text{-cm}$ ) are investigated. The benefit of introducing a thin conductive ( $\rho=0.5 \Omega\text{-cm}$ ) epitaxial layer below the oxide beneath metal strip in order to obtain a high quality factor and a high self-resonant frequency (SRF) is demonstrated. Finally, measurements of the newly developed inductor show a high quality factor of 22 at 30 GHz with the conductive epitaxial layer connected to ground. Moreover, an impressive measured SRF of 64 GHz is achieved for an inductor value of 0.75 nH.

### I. INTRODUCTION

Cost effective LMDS applications require single chip circuits up to 30 GHz. SiGe HBT technology can be able to satisfy this requirement [1]. Nevertheless, some troubles with passive elements, especially inductors on BiCMOS substrate, aren't overcome.

For millimeter wave monolithic integration on silicon, capacitors up to 1 pF are available but inductors generally feature too low self-resonant frequency and quality factor values, which lead to poor system performances.

This paper presents an in-depth investigation of monolithic inductors in order to get improved performances. The use of a thin epitaxial layer connected to ground is considered in order to obtain an excellent SRF and an improved quality factor. As an illustration of our approach, we report on the design of a rectangular inductor on BiCMOS substrate that exhibits enhanced performances.

To better understand the interest of this epitaxial layer, we first present the different types of losses, which take place in monolithic inductors on silicon, especially substrate losses. The second part focuses on the reduction of these substrate losses using an additional epitaxial layer below the inductor. Then we present experimental data obtained on inductors featuring different substrate layers configurations. Finally, a discussion addresses the position of our work with respect to the state-of-the-art for monolithic inductors on silicon.

### II. SUBSTRATE LOSSES

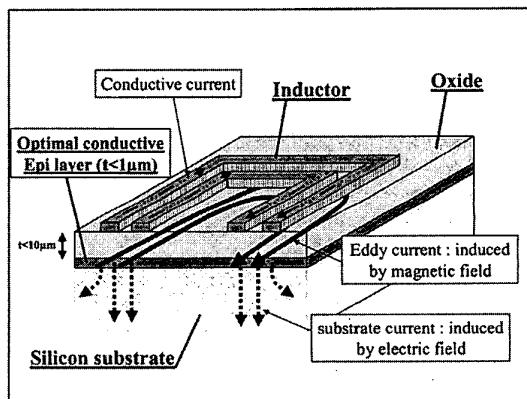

Different types of losses occur in monolithic inductors [2]. Figure 1 presents the three kinds of currents which take place in such a structure and which induce losses.

Figure 1 : Losses in monolithic inductors

First, ohmic losses appear in the conductor resulting in a quality factor proportional to  $f$  or  $f^\alpha$  ( $0 < \alpha < 1$ ) as the skin effect and the proximity effects take place in conductors according to frequency range. The minimization of these losses can mainly be achieved through the choice of the most conductive material for metal strip. This is the reason why technologies moved from aluminum to gold, and finally now to copper [3].

Secondly, losses also appear in the substrate as a consequence of both the electric field, which creates conductive current through the substrate, and the magnetic field which induces eddy currents. The resultant quality factors associated with these two types of losses are proportional to  $1/f$  and then abruptly decrease near the SRF. They depend on the substrate resistivity and also on the penetration of the fields into the semi-conductor.

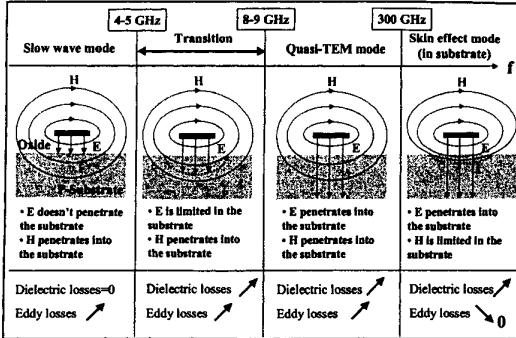

Figure 2 shows the different modes which can take place, according to the frequency, on a finite resistive substrate with a surface insulating oxide layer [4]. As illustrated, in

quasi TEM mode both electric and magnetic fields penetrate deep into the substrate whereas the electric field in the slow wave mode (low frequency), and magnetic field in the skin effect mode (high frequency) do not penetrate.

Figure 2: Different modes of propagation according to the frequency

Therefore, for commercial BiCMOS technology, the conventional passive elements realized over a few micrometers of oxide show a poor quality factor at microwave and millimeter wave frequencies due to the quasi-TEM mode which takes place in the substrate and the subsequent penetration of the E-field and H-field deep inside the substrate. Based on these considerations the next part presents a solution to circumvent these losses.

### III. OPTIMAL DESIGN

Two steps towards the optimization of inductor performances are addressed. The first one concerns the geometrical definition of inductors which influences both the SRF and the quality factor. The second one deals with the underlying layers configuration, which principally concern the quality factor.

To be able to operate at millimeter wave frequencies, inductors must feature a small strip width and a small out diameter in order to minimize the substrate volume occupied by the electromagnetic field and hence the consequent losses. Nevertheless, the resulting BiCMOS inductors exhibit only quality factor values below approximately 10 or 12 [5]. This quality factor is principally limited by substrate losses: the second step of our investigations addresses this issue.

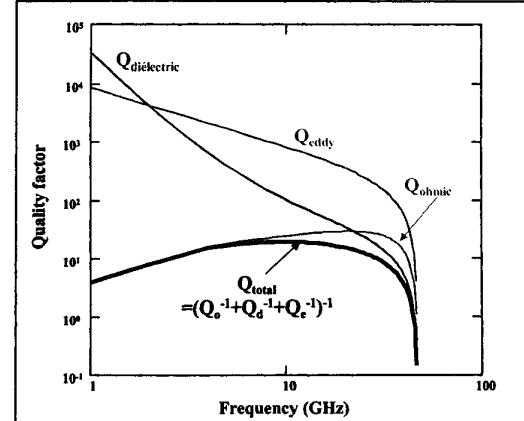

Figure 3 presents the variations versus frequency, computed from an electrical model of a 75 $\mu\text{m}$ -diameter-inductor [2], of the different quality factors associated to the different types of losses considered either independently each from the others or all together. The frequency range where each type of losses prevails can then be defined. For frequencies from 10 to 40-50GHz, the

dielectric losses are the major contributor to the total quality factor while the eddy losses do not contribute significantly over the whole frequency band. This is because of the small out-diameter value of the considered inductors, whereas eddy losses prevail over dielectric ones for taller inductors. So, minimizing substrate losses at millimeter-wave frequencies comes to decrease dielectric ones.

Figure 3 : Quality factors according to the frequency

One possible issue to reduce dielectric losses is to prohibit the electric field penetration in the substrate and therefore to enhance the slow-wave mode (see figure 2). This can be achieved by adding a thin (thickness  $t < 1 \mu\text{m}$ , depending on the frequency operation) epitaxial layer (named Nepi) over the bulk silicon substrate. The values of thickness  $t$  and resistivity  $\rho$  of this layer must fulfill relations (1) and (2) in order to warrant the slow wave mode [4].

$$\rho \ll \frac{h_{\text{ox}}}{t} \times \frac{1}{2\pi \epsilon_{\text{ox}} f_{\text{MAX}}} \quad (1)$$

$$t \ll \sqrt{\frac{\rho}{f_{\text{MAX}} \pi \mu_0}} \quad (2)$$

where  $h_{\text{ox}}$  and  $\epsilon_{\text{ox}}$  are respectively the thickness and the permittivity of the oxide layer and  $f_{\text{MAX}}$  is the maximal operating frequency.

The first condition warrants the slow wave mode operation into the Nepi layer and then prevents the penetration of electric field into the substrate.

The second condition guarantees the penetration of the magnetic field into the substrate layers and therefore warrants a maximum inductor value. This condition forbids the substitution of a metal for the Epi layer since this metal should feature an unachievable too small thickness.

Moreover, as eddy losses are negligible for small inductors with respect to the electric ones, it is not necessary to pattern the considered epitaxial layer in order to prevent the eddy currents as proposed in [6].

Electromagnetic simulations, conducted with Ansoft HFSS, qualitatively prove that the epitaxial layer limits the penetration of the electric field in the substrate and does not perturb the magnetic field. They therefore demonstrate the slow wave mode operation of the structure enclosing the conductive layer.

To resume, BiCMOS inductors realized over an oxide and a thin conductive (compared with the substrate) Nepi layer prohibits the penetration of the electric field in the substrate underneath without any consequence on the magnetic one. This cancels out most of the electric losses. The total resulting quality factor is then increased and becomes mainly limited by ohmic losses in the frequency band of interest. The maximal quality factor value can therefore be twice as much with respect to the one obtained without the Nepi layer as depicted in figure 3.

#### IV. RESULTS

The realized rectangular inductor, features 2.5 turns, an aluminum strip width of 5  $\mu\text{m}$ , a gap of 5  $\mu\text{m}$  and an out-diameter of 75  $\mu\text{m}$  and has been processed with the BiCMOS process from ST Microelectronics.

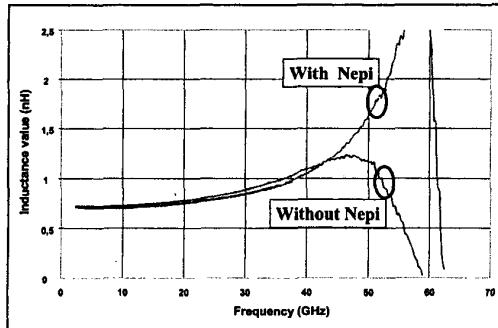

Two kinds of layers configurations are investigated: one involving the conductive epitaxial layer and the other one without this layer. Experimental results (figure 4) firstly show that the presence of the epitaxial layer or not has no impact of the inductance value over a large frequency range. This result demonstrates that the Nepi layer does not disturb the magnetic field. The value of the inductance is 0.75 nH, as shown in figure 4. Its SRF value is 64 GHz (in single end configuration).

Figure 4 : Measured inductance values vs frequency

In differential configuration, a SRF of 99 GHz is reached. This result is particularly attractive for millimeter-wave differential oscillators.

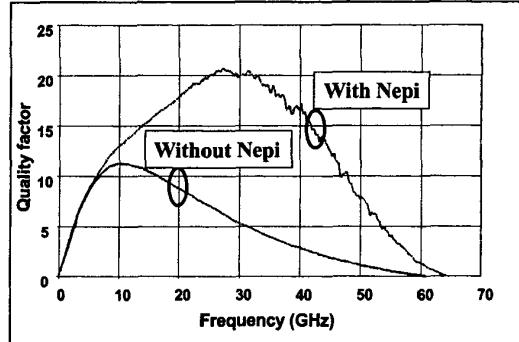

Figure 5 shows the quality factors for the two different layers configurations. Without the conductive epitaxial layer, a maximum quality factor of about 12 is reached at an optimal frequency of 10 GHz. With the epitaxial layer, the radical reduction of substrate dielectric losses translates into a higher maximum quality factor, which reaches 22, and simultaneously an impressive increase of the optimal frequency, which rises up to 30 GHz. This graph demonstrates the benefit of using the epitaxial layer and validates the model previously investigated.

Figure 5 : Measured quality factor values vs frequency

Finally, these experimental results show that monolithic inductors realized on BiCMOS substrate can reach an enhanced quality factor of 22 around 30 GHz with an impressive self-resonant frequency of 64 GHz, even if aluminum only is used for metallization. These excellent results are due to the presence of the thin conductive epitaxial layer, which is about 30 times more conductive than the substrate, features a thickness of about the skin depth and therefore prevents the electric field from penetrating through the resistive substrate without disturbing the magnetic field.

#### V. DISCUSSIONS

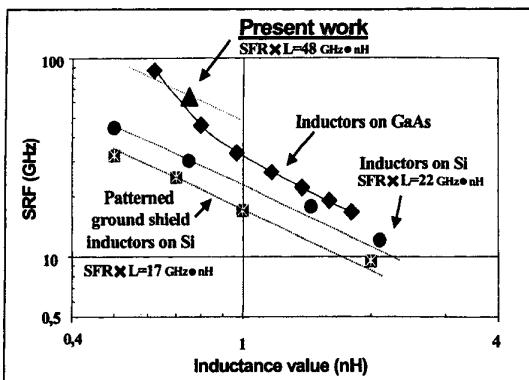

As an evaluation of our work, we compared different reported inductors realized with published BiCMOS technologies [3,5] and also on Gallium Arsenide substrate [7]. We compare the different SRF and the different quality factors.

As the SRF is inversely proportional to the inductor value  $L$ , we introduce the normalized parameter:  $\text{SFR} \times L$ . As depicted in figure 6, our inductor reaches a value of  $\text{SFR} \times L = 48 \text{ GHz} \times \text{nH}$ , which is twice than those of conventional inductors on silicon [3,5], with and without a patterned ground shield, and better than most of the GaAs ones.

## VI. CONCLUSION

This paper demonstrates that monolithic inductors realized with BiCMOS technology can be used up to the millimeter wave frequency domain with an excellent quality factor. Such improvements are obtained thanks to a thin conductive epitaxial layer connected to ground and above which the inductor is processed. A 0.75 nH inductor using this efficient and cost effective technique features a measured self resonant frequency of 64 GHz for a maximum quality factor of 22 at 30 GHz. Its differential SRF is 99 GHz with a differential quality factor of about 50, which is very attractive for spatial applications in order to realize low phase noise differential oscillator and translates, for example, into a predicted reduction of the phase noise from -87 dBc/Hz at 100kHz from carrier [1] to -100 dBc/Hz. These performances correspond to the state-of-the-art for millimeter wave frequency inductors on silicon substrate.

## ACKNOWLEDGMENT

The authors would like to thank D. Gloria and B. Van-Haaren, ST Microelectronics at Crolles-France, for their useful comments about this work.

## REFERENCES

- [1] S.P. Voinigescu, D. Marchesan and M.A. Copeland : "A family of monolithic inductor-varactor SiGe-HBT VCOs for 20GHz to 30GHz LMDS and fiber-optic receiver applications" *RFIC 2000*, pp170, 173.

- [2] John R. Long " integrating Passive Components and RF/MMIC Design ", BCTM 2000 Short course.

- [3] Joachim N. Burghartz "Status and Trends of Silicon RF Technology", *Technical Digest ESSDERC*, Sept. 13-15, 1999, Leuven, Belgium.

- [4] H. Hasegawa, M. Furukawa and H. Yanai " Properties of microstrip line on Si-SiO<sub>2</sub> system", *IEEE MTT-19* n°11 pp869-881, Nov. 1971.

- [5] Joachim N. Burghartz "Integrated Multilayer RF Passives in Silicon Technology", *Topical Meeting on Silicon monolithic integrated circuits in RF systems*, 17-18 sept 1998, Ann Arbor, Michigan pp 141-147.

- [6] Y.E. Chen, D. Bien, D. Heo, J. Laskar « Q-enhancement of spiral inductor with N<sup>+</sup>-diffusion patterned ground shields », *IEEE MTT-S digest 2001*, pp.1289-1292.

- [7] ED02AH Design Manual V200CD, *Philips Microwave Limeuil (OMMIC)*, April 1999.

- [8] C-Y Chi, G.M. Rebeiz, « Planar microwave and millimeter-wave lumped and coupled-line filters using micro-machining techniques », *IEEE MTT-43*, n°4 april 1995, pp.730-738.

Figure 6 : Normalized SRF according to inductor values

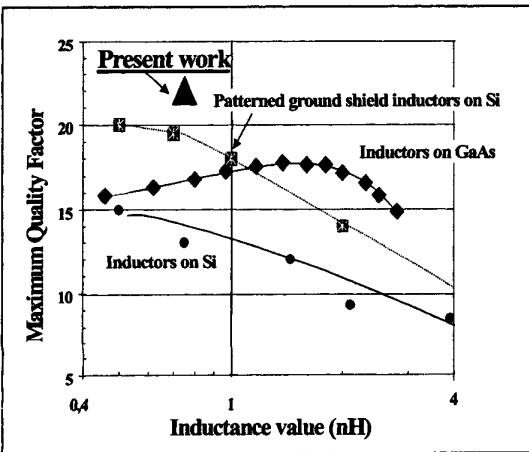

Finally, as presented in figure 7, the quality factor of our inductor is better than classical inductors both on silicon [3,5] and GaAs [7]. Only patterned ground shield inductors show similar values but they can't exhibit simultaneously a good SRF as shown in figure 6 (only a 23 GHz SRF for L=0.75 nH).

Figure 7 : Quality factors according to inductor values

The newly proposed inductor therefore sets the state-of-the-art since reported similar performances are, at that time, only achieved with micromachining techniques applied as post-processing [8]. Nevertheless, the technique we proposed does not involve additional step and uses only the conventional IC technological process.